BOSTON, July 24, 2024 /PRNewswire/ -- Over the past

decade, the capacity of data center Ethernet switches has

surged from 0.64 Tbps to 25.6 Tbps, driven by the adoption of

64x400 Gbps or 32x800 Gbps pluggable optical transceiver modules.

However, these high-speed modules, within their current form

factors, pose significant challenges. Issues include the required

densities of electrical and optical connectors, as well as

escalating power consumption.

To achieve next-generation optical engines supporting 800 Gbps

and beyond per module, the communication rate must double to at

least 100 Gbps per lane. This increase introduces substantial

signal integrity issues across the switch socket, motherboard, and

edge connector, leading to heightened power dissipation at SerDes

interfaces. In future Ethernet switching, these signal integrity

problems may cause I/O power consumption to exceed that of the

switch core. Additionally, the integration density of standard

pluggable modules is limited by the QSFP/OSFP form factor,

necessitating advanced thermal management solutions not yet widely

available.

Co-Packaged Optics (CPO) presents a promising solution to these

challenges. Unlike traditional pluggable models, CPO integrates

optical modules directly onto the switch ASIC substrate, reducing

electrical reach and effectively addressing signal integrity

issues. This approach has gained traction among major data centers.

However, optimizing the packaging strategy for CPO remains a topic

of ongoing industry discussion and development. IDTechEx's latest

report, "Co-Packaged Optics (CPO) 2025-2035: Technologies, Market,

and Forecasts", explores these advancements in CPO technology and

packaging techniques enabling its adoption.

The importance of advanced semiconductor packaging

technologies for Co-Packaged Optics (CPO)

The integration of CPO in data centers aims to boost I/O

bandwidth and reduce energy consumption. The way photonic

integrated circuits (PICs) are combined with electronic integrated

circuits (EICs) and switch ICs, can significantly influence the

areal and edge bandwidth density, as well as packaging parasitics.

These factors directly affect the transceiver's I/O bandwidth and

energy efficiency, meaning improper integration can negate the

advantages of silicon photonics.

For CPO, the integration of photonic and electronic components

can be achieved through various methods, each with unique

advantages and challenges. The most advanced, and still in the

R&D phase, is the 3D monolithic integration. This embeds

photonic components within an existing electronic process node with

minimal alterations, co-locating active photonics and driving

electronics within the same die. This reduces parasitics and

simplifies packaging by eliminating the need for interface pads and

bumps. However, monolithic integration typically uses older CMOS

nodes, resulting in suboptimal photonic performance and higher

energy consumption. Despite these limitations, it offers minimal

impedance mismatch and simplified packaging.

Conversely, 2D integration places the PIC and EIC side by side

on a PCB, connected by wire bonds or flip-chip. This method is

straightforward and cost-effective, but introduces significant

parasitic inductance, limiting aggregate I/O due to single-edge

connections. While 2D integration is easy to package, the reliance

on wire bonds constrains the transceiver bandwidth and increases

energy consumption, making it less efficient for high-performance

applications.

3D hybrid integration offers a more advanced solution by placing

the EIC on top of the PIC, via various advanced semiconductor

packaging technologies including Through-Si-Via (TSV), high density

fan-out, Cu-Cu hybrid bonding, and active photonic interposer,

significantly reducing parasitics. The use of advanced

semiconductor packaging technologies in 3D integration allows for

dense pitch capabilities, enhancing performance. However, thermal

dissipation remains a challenge, as the heat generated by the EIC

can impact the PIC, necessitating advanced thermal management

solutions. Despite these thermal challenges, 3D hybrid integration

achieves higher performance due to minimized packaging

parasitics.

2.5D integration serves as a compromise, with both the EIC and

PIC flip-chipped onto a passive interposer with TSVs. This approach

maintains manageable parasitics and dense pitch capabilities

similar to 3D integration but adds complexity with the need for

interposer traces. While 2.5D integration balances performance,

cost, and fabrication turnaround, it incurs higher parasitics than

3D hybrid integration.

In summary, each integration method presents trade-offs between

performance, complexity, and cost, with the choice based on

specific application requirements and constraints.

Co-Packaged Optics (CPO) market trajectory

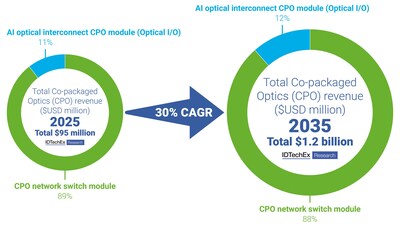

According to IDTechEx, the Co-Packaged Optics (CPO) market is

projected to exceed $1.2 billion by

2035, growing at a robust CAGR of 28.9% from 2025 to 2035. CPO

network switches are expected to dominate revenue generation,

driven by each switch potentially incorporating up to 16 CPO PICs.

Optical interconnects for AI systems will constitute approximately

20% of the market, with each AI accelerator typically utilizing one

optical interconnect PIC to meet increasing demands for high-speed

data processing and communication in advanced computing

applications.

IDTechEx's latest report, "Co-Packaged Optics (CPO) 2025-2035:

Technologies, Market, and Forecasts", offers extensive exploration

into the latest advancements within Co-Packaged Optics technology.

The report delves deep into key technical innovations and packaging

trends, providing a comprehensive analysis of the entire value

chain. It thoroughly evaluates the activities of major industry

players and delivers detailed market forecasts, projecting how the

adoption of CPO will reshape the landscape of future data center

architecture.

Central to the report is the recognition of advanced

semiconductor packaging as the cornerstone of Co-Packaged Optics

technology. IDTechEx places significant emphasis on understanding

the potential roles that various semiconductor packaging

technologies may play within the realm of CPO.

Key aspects of the report include:

- Market Dynamics: Examination of key players such as Nvidia,

Broadcom, Cisco, Ranovus, and Intel, and the forces shaping the CPO

landscape.

- Innovations in CPO Design: Exploration of advanced CPO designs

and their implications for enhancing data center efficiency and

shaping future architecture.

- Semiconductor Packaging Breakthroughs: Insight into the latest

advancements in semiconductor packaging, including 2.5D and 3D

technologies, and their role in enabling CPO innovation.

- Optical Engines: Analysis of the drivers behind CPO's

performance and efficiency advantages.

- CPO for AI Interconnects: Exploration of how optical I/O can

address the limitations of copper connections in AI applications,

improving efficiency, latency, and data rates.

- CPO for Switches: Assessment of the potential 25% efficiency

gains in high-performance network switches through CPO

integration.

- Challenges and Solutions: Critical review of obstacles to CPO

adoption and strategies to overcome them.

- Future Analysis: Predictions and insights into the next

generation of CPO and its anticipated impact on the industry.

The report is based on extensive research and interviews with

industry experts and provides valuable insights for anyone

interested in gaining a strategic understanding of Co-Packaged

Optics' role in advancing the future of data centers and AI

technology.

- Market Forecasts:

-

- 10-year Data Center Population Cumulative Forecast

- 10-year AI Accelerator Unit Shipments Forecast

- 10-year CPO Interconnect for AI (Optical I/O) Unit Shipments

Forecast

- 10-year CPO Interconnect for AI (Optical I/O) Market Revenue

Forecast

- 10-year CPO-enabled Network Switch Unit Shipments Forecast

- 10-year CPO-enabled Network Switch Market Revenue Forecast

- 10-year Total CPO Market Revenue

For more information on this IDTechEx report, including

downloadable sample pages, please visit www.IDTechEx.com/CPO.

For the full portfolio of related research available from

IDTechEx please see www.IDTechEx.com/Research/Semiconductors.

About IDTechEx

IDTechEx provides trusted independent research on emerging

technologies and their markets. Since 1999, we have been helping

our clients to understand new technologies, their supply chains,

market requirements, opportunities and forecasts. For more

information, contact research@IDTechEx.com or

visit www.IDTechEx.com.

Media Contact:

Charlotte Martin

Subscriptions Marketing Manager

press@IDTechEx.com

+44(0)1223 812300

Social Media Links:

X: https://www.twitter.com/IDTechEx

LinkedIn: https://www.linkedin.com/company/idtechex/

Photo:

https://mma.prnewswire.com/media/2468305/Total_CPO_Market_Growth.jpg

Logo: https://mma.prnewswire.com/media/478371/IDTechEx_Logo.jpg

View original

content:https://www.prnewswire.co.uk/news-releases/idtechex-discusses-co-packaged-optics-cpo-packaging-technology-trends-and-market-trajectory-302205422.html

View original

content:https://www.prnewswire.co.uk/news-releases/idtechex-discusses-co-packaged-optics-cpo-packaging-technology-trends-and-market-trajectory-302205422.html